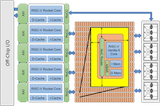

SoC Top : bsg_design

SoC Top : bsg_design

Package & PCB : http://bjump.org

Package & PCB : http://bjump.org

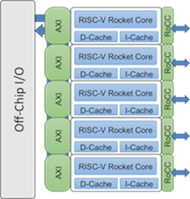

General Purpose Tier

A few fully featured RISC-V processors capable of running general-purpose software including an operating system. Modified version of Berkeley Rocket core.

- Rocket : bsg_rocket

- RoCC Doc: RoCC Doc V2

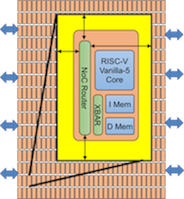

Massive Parallel Tier

A manycore comprising hundreds of lightweight RISC-V processors, a distributed shared memory system, and a mesh-based interconnect.

- BaseJump Manycore: bsg_manycore

- BaseJump STL: bsg_ip_cores

- Celerity QuickStart Tutorial

Specialization Tier

Application-specific accelerators (possibly generated using high-level synthesis).

- BNN FPGA: bnn-fpga